nxAccess

Our FPGA-powered trading engine

nxAccess is a trading engine with an FPGA algo sandbox allowing users to preload orders in hardware, receive market data then trigger & update those orders before sending to the trading venue – with the speed and performance of hardware assisted by the flexibility of software.

With constant, deterministic, and jitter-free performance, nxAccess offers the power of FPGA technology with the integration simplicity of a software solution.

Designed for market making, high performance trading and arbitrage strategies, nxAccess accelerates existing trading algorithms without the investment usually required for FPGA-enabled performance.

Download BrochurenxAccess Execution Engine

Preload, Trigger, Update, Send

A unique feature of the nxAccess solution is the ability to leverage hardware for latency critical strategies while maintaining the flexibility of software ensuring a smooth transition to FPGA technology.

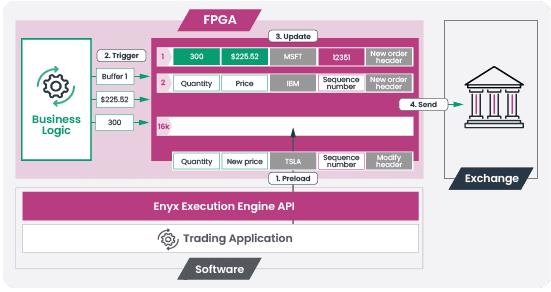

The Enyx Execution Engine enables software applications to manage the order execution protocol and FPGA logic to trigger and send orders to the exchange in the following sequence:

Orders or templates of orders are preloaded by software into the execution engine buffers.

Hardware business logic uses market data or order fill notification to request the trigger of a preloaded buffer & provide fields to update the order.

Once triggered, the selected buffer is updated with fields from the hardware business logic & any required variables previously initialized by the software.

The fully updated order is sent to the exchange.

Performance Reports

Hardware Tick-to-Trade w/ Pattern matcher

389 ns*

Hardware Tick-to-Trade w/o Pattern matcher

624 ns*

Software Tick-to-Trade

1.5 µs*

*SOP-to-SOP latency measured on the switch for the Chicago Mercantile Exchange (CME)

Fully integrated FPGA-based market data processing

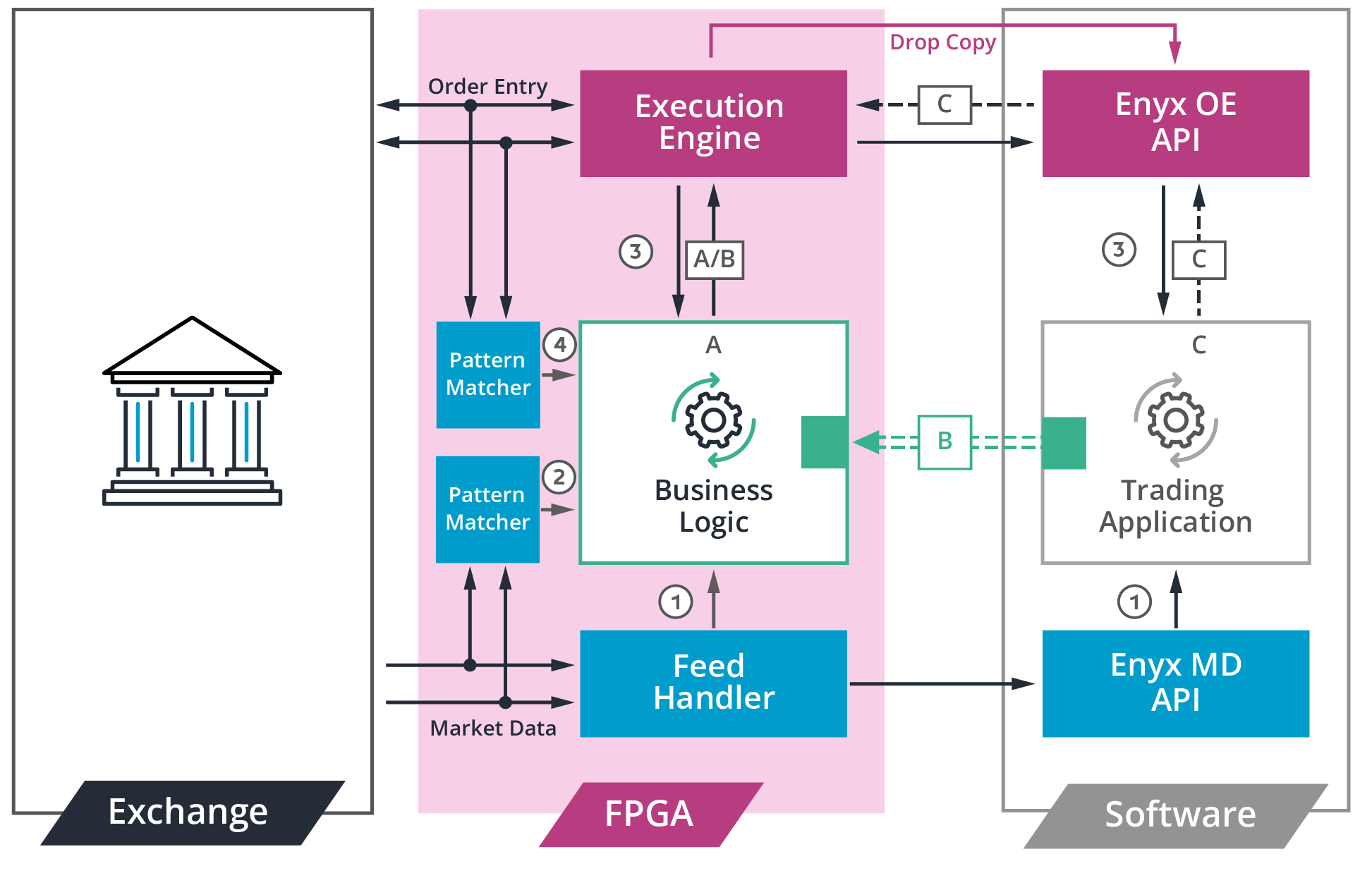

To accommodate a wide range of trading strategies with varying latency profiles, nxAccess provides two paths to deliver and process incoming market data.

An embedded FPGA-based feedhandler with order book building allows algorithms to make trading decisions based on the most complete view of the market.

Additionally, pattern matcher functionality within nxAccess provides a raw market data decoder which quickly extracts key values, such as prices or quantities, allowing users to implement ultra-low latency trading strategies using lightweight market data processing.

Supported Markets

nxAccess: FPGA-based Trading Engine

Hardware performance with software flexibility

nxAccess uses a hybrid implementation with an FPGA data path for latency critical logic and an accelerated software data path for more complex and less latency sensitive logic.

- Normalized market data – the FPGA feed handler arbitrates, decodes, normalizes and builds order books for all subscribed symbols. Delivers normalized data to both hardware & software trading logic.

- Raw market data – the pattern matcher extracts specific signals (i.e. trade summaries) without normalization, bypassing the feed handler, to further reduce latency. Delivers raw data to hardware trading logic only.

- Order fill notifications – the execution engine receives incoming order fill notifications from the exchange. Delivers raw data to both hardware & software trading logic.

- Hardware trigger (HLS or HDL)

- Provides easy-to-use, low latency interface to the hardware algorithm.

- Software trigger (C++)

- Uses the same interface as the hardware trigger, allowing for software emulation of hardware business logic (example bus + reference firmware).

- Hardware trigger can detect duplicate/delayed triggers from software and react accordingly

- Direct send via software trading application (C++)

- Simple software only path for non-latency sensitive applications

nxAccess: The Pattern Matcher

Hardware performance with software flexibility

nxAccess uses a hybrid implementation with an FPGA data path for latency critical logic and an accelerated software data path for more complex and less latency sensitive logic.

- Users can configure the fields and messages that the decoders will extract

- Ultra low latency decoders receive raw market data directly from the MAC/PCS and are both protocol & message aware – allowing for reliable and accurate field extraction

- Price & instrument normalization can be removed to further reduce latency

- Pattern matcher provides field updates to the trading logic via a tag/value bus

Specifications

- Supports up to 8000 symbols

- Symbols / Message type / Book depth filtering

- A/B feed arbitration by message

- Book-based and/or order-based market data updates

- Market data & order execution exchange resynchronization

- Full Hardware TCP Stacks

- 2 MBytes of in-FPGA order storage

- Up to 16 000+ order buffers

- Orders can be stored one-by-one or in bulk

- Order MTU up to 1504 Bytes

- Kill switch with software heartbeat & bandwidth watchdog

- Aggregated Rx/Tx audit trail

- Monthly performance & EDC updates

Related Resources

3 Ways Market Data-as-a-Service Can Protect Your Business

Yesterday’s Infrastructure is Today’s Financial Loss Skyrocketing message rates and frequent exchange changes push traditional market data systems to their limits. Market data-as-a-Service offers an alternative approach. Outsourcing infrastructure management…

Level 2 Market Data: What Level Supports Your Trading Strategy?

Know what market data you use and how it fits within your firm’s strategy to ensure proper market data budgeting.

How Market Data Fees Can Inform Your Infrastructure Plans

Market data is the third largest expense for many banks and broker-dealers. Understanding fees can help firms with infrastructure planning and budgeting.